# ST(意法) BAL-NRF01D3 PDF

# 深圳创唯电子有限公司

http://www.st-ic.com

## **BAL-NRF01D3**

# 50 $\Omega$ nominal input / conjugate match balun to nRF51422-QFAA, nRF24LE1, nRF51822-QFAA/AB, with integrated harmonic filter

Datasheet - production data

#### **Features**

- 50 Ω nominal input / conjugate match to Nordic Semiconductor chips nRF24LE1 QFN32, nRF24AP2-1CH, nRF24AP2-8CH, nRF51422-QFAA (build code CA/C0), nRF51822-QFAA (build code CA/C0) and nRF51822-QFAB (build code AA/A0)

- Low insertion loss

- Low amplitude imbalance

- Low phase imbalance

- Small footprint < 1.5 mm<sup>2</sup>

#### **Benefits**

- Very low profile < 595 μm after reflow</li>

- High RF performance

- RF BOM and area reduction

#### **Applications**

- 2.45 GHz impedance matched balun filter

- Optimized for Nordic's chip set nRF24LE1/AP2, nRF51422-QFAA (build code CA/C0), nRF51822-QFAA (build code CA/C0) and nRF51822-QFAB (build code AA/A0)

#### **Description**

STMicroelectronics BAL-NRF01D3 is an ultraminiature balun. The device integrates matching network and harmonics filter. Matching impedance has been customized for the following Nordic Semiconductor circuits: nRF24LE1 QFN-32 pins, nRF24AP2-1CH, nRF24AP2-8CH, nRF51422-QFAA (build code CA/C0), nRF51822-QFAA (build code CA/C0) and nRF51822-QFAB (build code AA/A0).

The device uses STMicroelectronics' IPD technology on a non-conductive glass substrate to optimize RF performance.

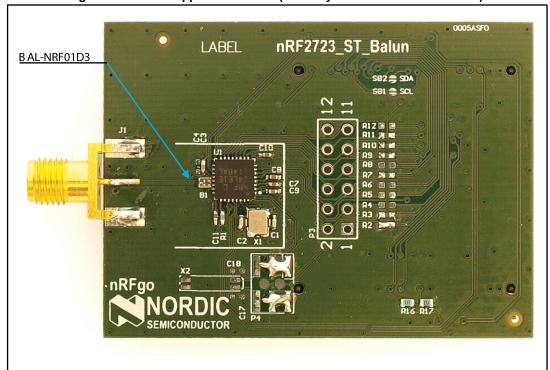

The BAL-NRF01D3 has been tested and approved by Nordic Semiconductor in their nRF2723 and nRF2752 nRFgo modules.

Characteristics BAL-NRF01D3

### 1 Characteristics

Table 1: Absolute maximum ratings (limiting values)

| Symbol           | Parameter                                                                   |      | Unit |      |       |  |

|------------------|-----------------------------------------------------------------------------|------|------|------|-------|--|

| Symbol           | Farameter                                                                   | Min. | Тур. | Max. | Oiiit |  |

| Pin              | Input power RFIN                                                            |      | -    | 20   | dBm   |  |

|                  | ESD ratings MIL STD883C (HBM: C = 100 pF, R = 1.5 $\Omega$ , air discharge) | 2000 | -    |      |       |  |

| V <sub>ESD</sub> | ESD ratings charge device model (JESD22-C101-C)                             | 500  |      |      | V     |  |

|                  | ESD ratings machine model (MM: C = 200 pF, R = 25 W, L = 500 nH)            | 200  | -    |      |       |  |

| T <sub>OP</sub>  | Operating temperature -40 - +105                                            |      |      |      |       |  |

Table 2: Impedances (T<sub>amb</sub> = 25 °C)

| Symbol          | Parameter                             | Value     |                                                                                                                                         |      |      |

|-----------------|---------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Symbol          | Parameter                             | Min. Typ. |                                                                                                                                         | Max. | Unit |

| Zouт            | Nominal differential output impedance | -         | Conjugate match to:  nRF24LE1/AP2  nRF51422-QFAA (build code CA/C0)  nRF51822-QFAA (build code CA/C0)  nRF51822-QFAB (build code AA/A0) | -    | Ω    |

| Z <sub>IN</sub> | Nominal input impedance -             |           | 50                                                                                                                                      | -    | Ω    |

Table 3: RF performance (T<sub>amb</sub> = 25 °C)

| porternation (Tunio 20 0) |                                       |                |       |      |      |       |  |

|---------------------------|---------------------------------------|----------------|-------|------|------|-------|--|

| Symbol                    | Parameter                             | Test condition | Value |      |      | Unit  |  |

| Symbol                    | Farameter                             | rest condition | Min.  | Тур. | Max. | Oilit |  |

| F                         | Frequency range (bandwidth) 2400 2540 |                | 2400  |      | 2540 | MHz   |  |

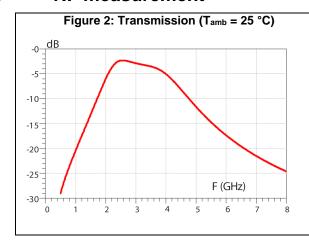

| IL                        | Insertion loss in bandwidth           |                |       | 2.25 |      | dB    |  |

| RL                        | Return loss in bandwidth              |                |       | 10   |      | dB    |  |

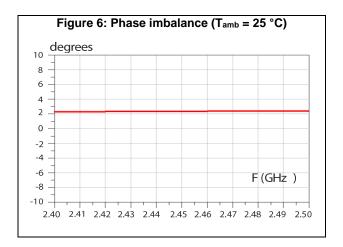

| фimb                      | Phase imbalance                       |                |       | 3    |      | 0     |  |

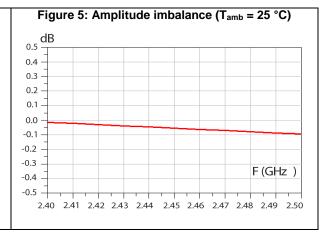

| Aimb                      | Amplitude imbalance                   |                |       | 0.1  |      | dB    |  |

| 2f0                       | 2nd harmonic filtering                | 4880 MHz       |       | 10   |      | dB    |  |

| 3f0                       | 3rd harmonic filtering 7320 MHz 20    |                |       | dB   |      |       |  |

BAL-NRF01D3 Characteristics

#### 1.1 RF measurement

Figure 3: Return loss on SE port (T<sub>amb</sub> = 25 °C)

-5

-7.5

-10

-12.5

-15

2.40 2.41 2.42 2.43 2.44 2.45 2.46 2.47 2.48 2.49 2.50

Figure 4: Return loss on DIFF port (T<sub>amb</sub> = 25 °C)

-20 dB

-25 -30 -35 -40 -45 -240 2.41 2.42 2.43 2.44 2.45 2.46 2.47 2.48 2.49 2.50

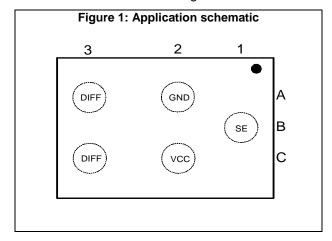

## 2 Application information

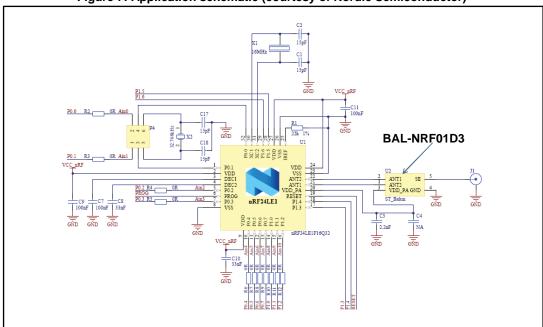

Figure 7: Application schematic (courtesy of Nordic Semiconductor)

Figure 8: nRF2723 application board (courtesy of Nordic Semiconductor)

BAL-NRF01D3

INFO

Figure 9: nRF2752 application board (courtesy of Nordic Semiconductor)

Package information BAL-NRF01D3

## 3 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

- Epoxy meets UL94, V0

- Lead-free package

### 3.1 Flip-Chip 5 bumps package information

Figure 10: Flip-Chip 5 bumps package outline

Table 4: Flip-Chip 5 bumps dimensions

| Parameter | Description                                     | Min.        | Тур. | Max. | Unit |

|-----------|-------------------------------------------------|-------------|------|------|------|

| Х         | X dimension of the die                          | 1445        | 1485 | 1525 | mm   |

| Υ         | Y dimension of the die                          | 980         | 1020 | 1060 | mm   |

| Α         | X pitch                                         |             | 604  |      | mm   |

| В         | Y pitch                                         |             | 500  |      | mm   |

| A1        | Distance from bump to edge of die on X axis 224 |             |      |      |      |

| B1        | Distance from bump to edge of die on Y axis 260 |             |      |      |      |

| A2        | Distance from VCC bump to SE bump on X axis 433 |             |      |      |      |

| B2        | Distance from bump to edge of die on Y axis 510 |             |      |      |      |

| С         | GND, VCC bump to SE bump pitch 500              |             |      |      |      |

| D         | Bump diameter                                   | 240         | 255  | 260  | mm   |

| T1        | Substrate thickness 425                         |             |      | mm   |      |

| Н         | Bump height 205 r                               |             |      |      | mm   |

| Т         | Total die thickness                             | 570 630 690 |      |      |      |

BAL-NRF01D3 Package information

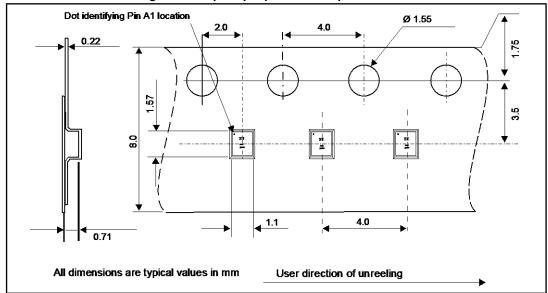

### 3.2 Flip-chip 5 bumps packing information

Dot, ST logo

ECOPACK grade

xx = marking

z = manufacturing

location

yww = datecode

Figure 15: Marking

X X Z

Y W W

Package information BAL-NRF01D3

Figure 16: Flip Chip tape and reel specifications

More packing information is available in the application note:

- AN2348 Flip-Chip: "Package description and recommendations for use"

- AN4111: "BAL-NRF01D3 matched balun with integrated harmonics filter for Nordic Semiconductor chips with ultralow power transceivers"

BAL-NRF01D3 Ordering information

## 4 Ordering information

**Table 5: Ordering information**

| Order code  | Marking | Package                     | Weight  | Base qty. | Delivery mode |

|-------------|---------|-----------------------------|---------|-----------|---------------|

| BAL-NRF01D3 | SC      | Flip-Chip package (5 bumps) | 1.82 mg | 5000      | Tape and reel |

## 5 Revision history

**Table 6: Document revision history**

| Date        | Revision | Changes                                                                                             |  |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------|--|--|

| 15-Oct-2012 | 1        | First issue.                                                                                        |  |  |

| 13-Nov-2012 | 2        | Added references to nRF51 series. Added Figure 9. Updated y-axis labels in Figure 2.                |  |  |

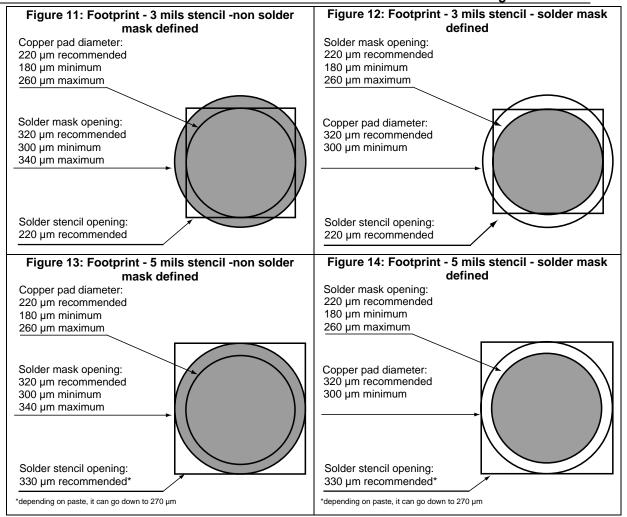

| 04-Mar-2013 | 3        | Updated footprint illustrations in Figure 13, and Figure 14.                                        |  |  |

| 06-Aug-2013 | 4        | Added dimensions in Figure 10. Updated marking orientation in Figure 11 and Figure 12.              |  |  |

| 13-Jan-2014 | 5        | Updated document title and product references.                                                      |  |  |

| 07-Jul-2015 | 6        | Updated Table 1.                                                                                    |  |  |

| 21-Jun-2017 | 7        | Updated Figure 10: "Flip-Chip 5 bumps package outline" and Table 4: "Flip-Chip 5 bumps dimensions". |  |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved